Journal of Engineering Research and Reports

20(5): 41-45, 2021; Article no.JERR.67343 ISSN: 2582-2926

# Die Placement Performance Evaluation on Different Machine Platforms

Rennier Rodriguez<sup>1</sup>, Edwin Graycochea Jr.<sup>1</sup> and Frederick Ray Gomez<sup>1\*</sup>

<sup>1</sup>New Product Development and Introduction, STMicroelectronics, Inc. Calamba City, Laguna, 4027, Philippines.

#### Authors' contributions

This work was carried out in collaboration amongst the authors. All authors read, reviewed and approved the final manuscript.

#### Article Information

DOI: 10.9734/JERR/2021/v20i517310 <u>Editor(s):</u> (1) Prof. Hamdy Mohy El-Din Afefy, Pharos University, Egypt. (2) Prof. David Armando Contreras-Solorio, Autonomous University of Zacatecas, Mexico. <u>Reviewers:</u> (1) Alberto Turón Lanuza, University of Zaragoza, Spain. (2) Qi Zeng, Shenzhen University, China. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/67343</u>

Original Research Article

Received 08 February 2021 Accepted 16 April 2021 Published 17 April 2021

#### ABSTRACT

The paper focuses on the die placement tolerance capability with critical design for land grid array (LGA) device evaluated on two different die attach machine platforms. The evaluation was narrowed down into two main die attach machines with the objective of attaining the best performance in terms of die placement tolerance capability. Die placement tolerance were quantified and only die attach Machine B was able to satisfy the specification of less than 30 microns. The study used a bar graph comparison in terms of die placement tolerance on the two machines and presented the effect of machine selection on die placement tolerance capability. For future works, the selected die attach machine could be used for devices with critical requirement.

Keywords: Die attach process; die placement; LGA; substrate package.

#### **1. INTRODUCTION**

Land grid array (LGA) substrate packaging technologies are continuously developed and improved to deliver high quality and robust

products for various applications. A common direction of semiconductor manufacturing companies is to increase the manufacturing yields and maintain high quality while minimizing the wastage and assembly rejections. With the

\*Corresponding author: Email: f.i.gomez@ieee.org, frederick-ray.gomez@st.com;

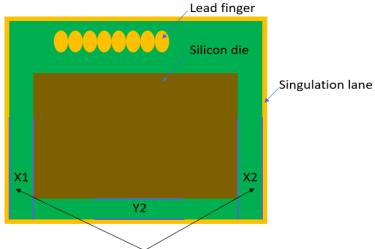

new and continuous technology trends and breakthroughs, challenges assembly in manufacturing are unavoidable [1-4]. In this paper, a LGA device is identified to be critical due to the die placement tolerance capability with critical design. When the package has a requirement with tight tolerances, the die placement must be placed properly on the carrier or substrate using the process of die attach. Die attach is a process responsible in the process of picking and bonding an individually sawn silicon die from a wafer tape to the carrier. Fig. 1 shows the representation of the device with critical die placement. To guarantee its integrity, during production run, die attach process is incorporated with multiple criteria such as, die placement, bond line thickness, die shear test, peel off and epoxy voids. Die placement is a critical criterion in die attach process because this can check the actual die placement requirement of the device and to verify if the machine can meet the die placement requirement.

#### 2. REVIEW OF RELATED LITERATURE

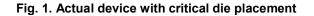

Assembly process flow for LGA device is shown in Fig. 2 highlighting the assembly process in focus. Important to note that assembly process flow changes with the product and the technology. Also as previously mentioned, new technologies and breakthroughs bring along its many challenges.

Die attach assembly process is the method of attaching a silicon die or multiple dice on a leadframe carrier. The method of attaching the die to a carrier is formed using the sequence: 1) the ejector needle ejects up the semiconductor die from the wafer tape; 2) the rubber-tip picks the die from the needle; 3) the picked die is placed on the already dispensed leadframe or directly on the die paddle for die attach film; 4) the bonding height is determined by the bonding parameter with together the dispense configuration. Die attach film (DAF) die bonding uses an adhesive called DAF to attach the silicon die on the substrate. Based on the standard operating procedure, it must pass or satisfy all the necessary buy-off requirement prior run the actual lot.

Die placement on LGA device are critically monitored as this may lead to exposed die on the package. Exposed die in semiconductor packages often happens within the package itself, which caused by shifting the silicon die outside the required die placement tolerance capability on the desired machine. Exposed die is detected during the cutting of units individually at singulation process.

Usually, a tight die placement and its tolerance is necessary on devices with very tight design clearances. Tight clearance in a semiconductor package is a big challenge in assembly manufacturing especially for the very small packages. Clearance is a critical factor during IC assembly since the distances/spaces between individual parts are used to anticipate the variation or deviation produced by the individual process step during assembly [4-7]. Moreover, each assembly process is affected by the equipment and material tolerances.

## 3. METHODOLOGY

The LGA device was evaluated in two different die attach machine platforms for critical design to meet the die placement tolerance capability. Machine A is an older version that has a tolerance capability of 50  $\mu$ m (microns) using a DAF as a material. The large tolerance means that the die placement is not stable or robust during the attachment or bonding of die on the substrate. In contrast, Machine B is capable to achieve 30 microns die placement tolerance, which is relatively better than previous one.

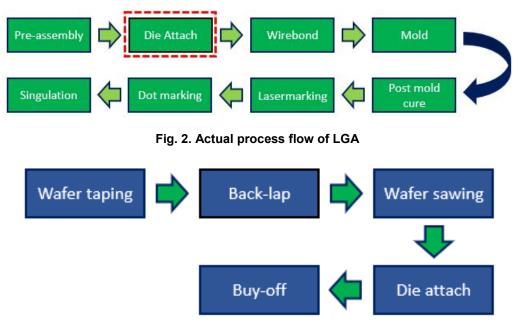

The data gathering flow is defined in Fig. 3. The wafer is taped to protect the front side layer during back lap process. The wafer is then grinded to 70 microns final die thickness. The sawn dice of 2.7 x 1.7 mm<sup>2</sup> die size taped in wafer ring are later transferred to die attach station for setup and optimization. The bonded units are then subjected pc buyoff, to check all the gating criteria are meet especially for the die placement requirement.

#### 4. RESULTS AND DISCUSSION

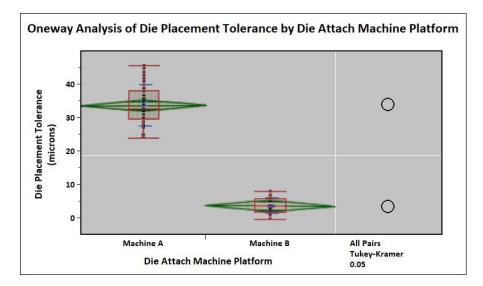

The analysis of variance on the die placement tolerance of the two machine platforms is shown in Fig. 4 with 30 sample units each. The All Pairs Tukey-Kramer test is used to show and find means or average that are significantly different to each other. And visually it shows in the graph through the 2 circles that far away from each other and not intersecting signifying there is significant difference on the two die attach machines with regards to the die placement tolerance performance. Based on the results, Machine A has a high movement of die placement greater than 34 microns mean versus the maximum specification of less than 25 microns defined in the assembly internal specification. Machine B has a good die placement tolerance capability with less than 10 microns. The lower the die placement tolerance the lower movement of the die during die bonding. Note that the die placement is measured manually by microscope measuring machine. Normally, the measurement is based on the mount bonding diagram (MBD) if there is a specific measured requirement. Machine B was able to run this type of new technology with critical criteria on the die placement tolerance capability with an average of 6 microns compared to Machine A.

X1/X2 with critical die placement

Fig. 3. Data gathering flow

Fig. 4. Statistical analysis of die placement tolerance on two die attach machine

## 5. CONCLUSION AND RECOMMEND-ATIONS

The paper discussed the evaluation of different machine platforms where to run the critical devices with tight die placement tolerance capability especially for LGA devices. In this study, it has been shown that Machine B has a significant difference in attaining the best die placement tolerance capability. In turn, Machine B is capable for critical and tight die placement requirement especially for the newer semiconductor packaging technologies. For future works, Machine B could be used for such devices with tight die placement requirement. With regards to the die attach assembly process robustness and optimization, works and learnings shared in [8-12] are really helpful.

## DISCLAIMER

The products used for this research are commonly and predominantly used products in our area of research and country. There is absolutely no conflict of interest between the authors and producers of the products because we do not intend to use these products as an avenue for any litigation but for the advancement of knowledge. Also, the research was not funded by the producing company rather it was funded by personal efforts of the authors.

### ACKNOWLEDGEMENT

The authors are greatly thankful to the New Product Development & Introduction (NPD-I)

colleagues and the Management Team for the solid support.

#### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

## REFERENCES

- 1. Tsukada Y, et al. Trend of semiconductor packaging, high density and low cost. Proceedings of the 4th International Symposium on Electronic Materials and Packaging. Taiwan. 2002;1-6.

- Xian TS, Nanthakumar P. Dicing die attach challenges at multi die stack packages. 35th IEEE/CPMT International Electronics Manufacturing Technology Conference (IEMT). Malaysia. 2012;1-5.

- Sumagpang Jr. A, Rada A. A systematic approach in optimizing critical processes of high density and high complexity new scalable device in MAT29 risk production using state-of-the-art platforms. Presented at the 22nd ASEMEP Technical Symposium, Philippines; 2012.

- Yeap LL. Meeting the assembly challenges in new semiconductor packaging trend. 34th IEEE/CPMT International Electronic Manufacturing Technology Symposium (IEMT). Malaysia. 2010;1-5.

- 5. Coombs C, Holden H. Printed circuits handbook. 7th ed., McGraw-Hill Education, USA; March; 2016.

- Gomez FR, et al. Interconnect technique for tight clearance in stacked-die package. Journal of Engineering Research and Reports. 2020;11(2);1-5.

- May GS, Spanos CJ. Fundamentals of semiconductor manufacturing and process control. 1st ed, Wiley-IEEE Press, USA; 2006.

- Abdullah S, et al. Dicing die attach film for 3D stacked die QFN package. 32nd IEEE/CPMT International Electronic Manufacturing Technology Symposium (IEMT). USA. 2007;73-75.

- Buenviaje Jr. S, et al. Process optimization study on leadframe surface enhancements for delamination mitigation. IEEE 22nd Electronics Packaging Technology

Conference (EPTC). Singapore. 2020;95-100.

- 10. Rodriguez R, et al. A study of dispense needle for die attach voids mitigation. Journal of Engineering Research and Reports. 2020;14(1);25-29.

- Abdullah Z, et al. Die attach capability on ultra thin wafer thickness for power semiconductor. 35th IEEE/CPMT International Electronics Manufacturing Technology Conference. Malaysia. 2012;1-5.

- 12. Bacquian BC, et al. Bond line thickness characterization for QFN package robustness. Journal of Engineering Research and Reports. 2020;14(2);15-19.

© 2021 Rodriguez et al.; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

> Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/67343